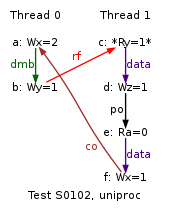

ARM S0102

"DMBdWW Rfe DpDatadW PodWR DpDatadW Wse"

Cycle=Rfe DpDatadW PodWR DpDatadW Wse DMBdWW

Relax=[Wse,DMBdWW,Rfe]

Safe=PodWR DpDatadW

Prefetch=0:x=F,0:y=W,1:y=F,1:x=W

Com=Rf Ws

Orig=DMBdWW Rfe DpDatadW PodWR DpDatadW Wse

{

%x0=x; %y0=y;

%y1=y; %z1=z; %a1=a; %x1=x;

}

P0 | P1 ;

MOV R0,#2 | LDR R0,[%y1] ;

STR R0,[%x0] | EOR R1,R0,R0 ;

DMB | ADD R1,R1,#1 ;

MOV R1,#1 | STR R1,[%z1] ;

STR R1,[%y0] | LDR R2,[%a1] ;

| EOR R3,R2,R2 ;

| ADD R3,R3,#1 ;

| STR R3,[%x1] ;

Observed

1:R0=1; x=2;