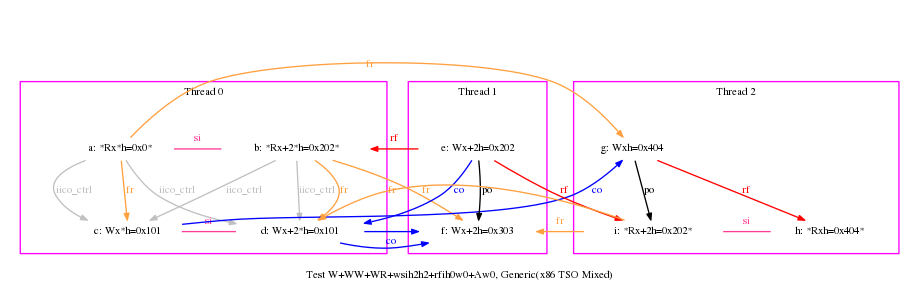

X86_64 W+WW+WR+wsih2h2+rfih0w0+Aw0

"WseAw0h2 Wsih2h2 Wseh2h0 Rfih0w0 Frew0Aw0"

Cycle=Rfih0w0 Frew0Aw0 WseAw0h2 Wsih2h2 Wseh2h0

Generator=diyone7 (version 7.54+05(dev))

Com=Ws Ws Fr

Orig=WseAw0h2 Wsih2h2 Wseh2h0 Rfih0w0 Frew0Aw0

{

0:rax=0x1010101;

1:rax=x;

}

P0 | P1 | P2 ;

movl %eax,%ebx | movw $514,2(%rax) | movw $1028,(x) ;

xchgl (x),%ebx | movw $771,2(%rax) | movl (x),%eax ;

Observed

x=0x3030404; 2:rax=0x2020404; 0:rbx=0x2020000;