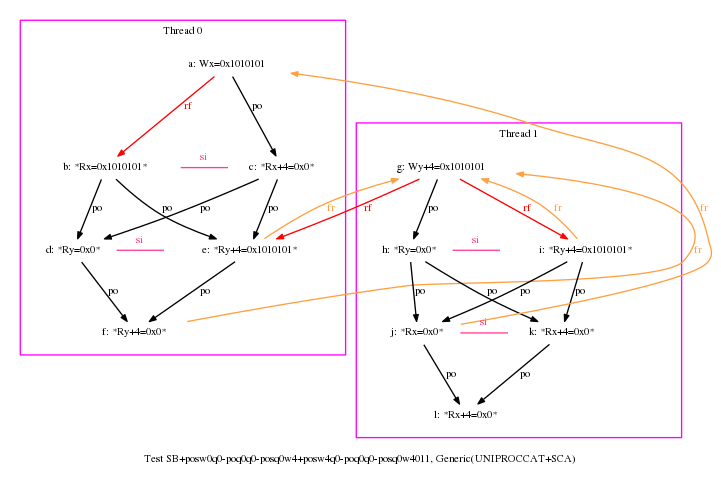

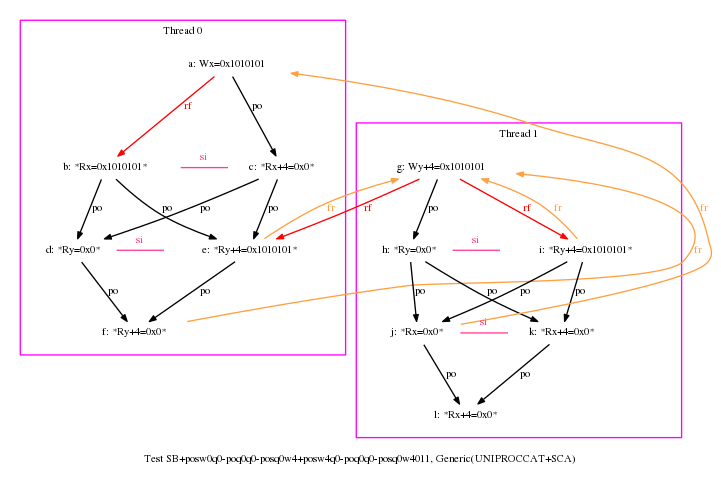

AArch64 SB+posw0q0-poq0q0-posq0w4+posw4q0-poq0q0-posq0w4011

"PosWRw0q0 PodRRq0q0 PosRRq0w4 Frew4w4 PosWRw4q0 PodRRq0q0 PosRRq0w4 Frew4w0"

Cycle=PosWRw0q0 PodRRq0q0 PosRRq0w4 Frew4w4 PosWRw4q0 PodRRq0q0 PosRRq0w4 Frew4w0

Relax=[PosWRw0q0,PodRRq0q0,PosRRq0w4] [PosWRw4q0,PodRRq0q0,PosRRq0w4]

Safe=Frew4w0 Frew4w4

Prefetch=0:x=F,0:y=T,1:y=F,1:x=T

Com=Fr Fr

Orig=PosWRw0q0 PodRRq0q0 PosRRq0w4 Frew4w4 PosWRw4q0 PodRRq0q0 PosRRq0w4 Frew4w0

{

uint64_t y; uint64_t x; uint64_t 1:X5; uint64_t 1:X3; uint64_t 1:X2; uint64_t 0:X5; uint64_t 0:X3; uint64_t 0:X2;

0:X0=0x1010101; 0:X1=x; 0:X4=y;

1:X0=0x1010101; 1:X1=y; 1:X4=x;

}

P0 | P1 ;

STR W0,[X1] | STR W0,[X1,#4] ;

LDR X2,[X1] | LDR X2,[X1] ;

LDR X3,[X4] | LDR X3,[X4] ;

LDR W5,[X4,#4] | LDR W5,[X4,#4] ;

Observed

y=0x101010100000000; x=0x1010101; 1:X5=0x0; 1:X3=0x0; 1:X2=0x101010100000000; 0:X5=0x0; 0:X3=0x101010100000000; 0:X2=0x1010101;