…

…

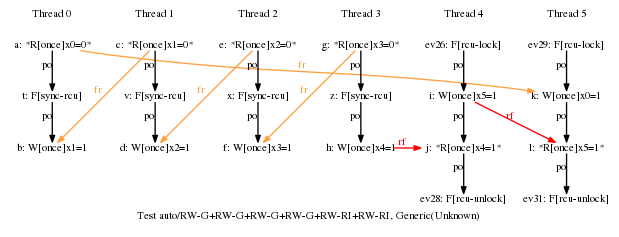

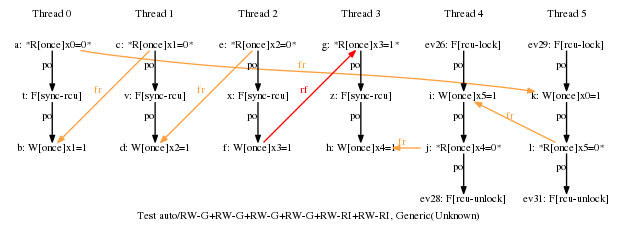

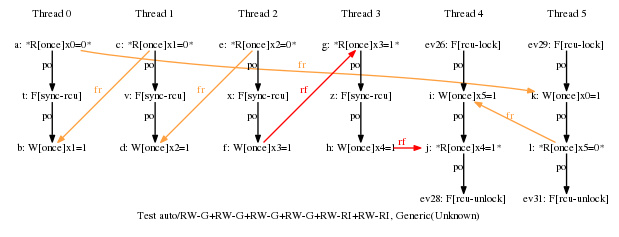

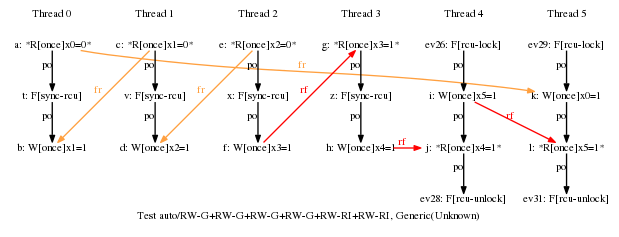

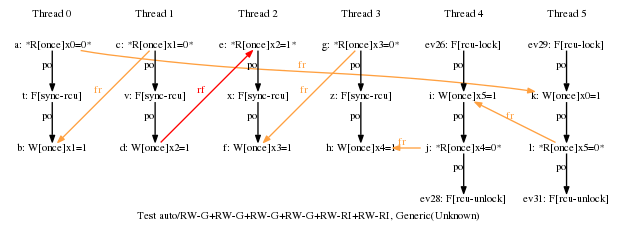

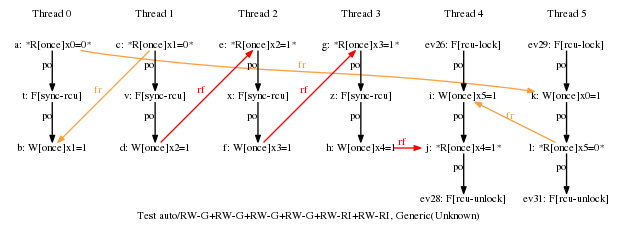

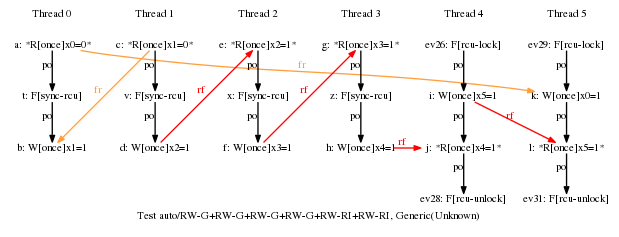

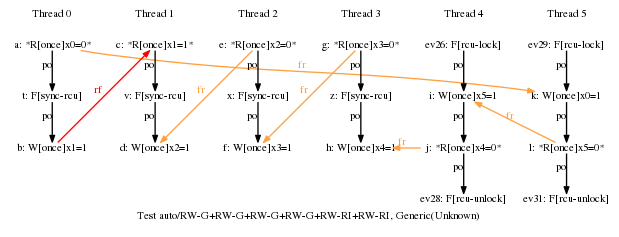

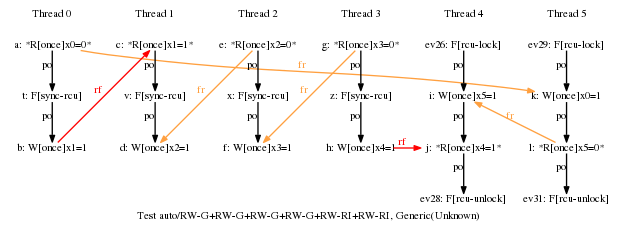

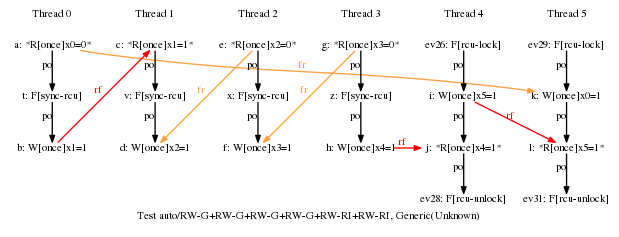

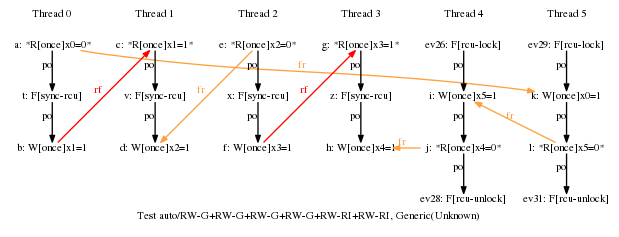

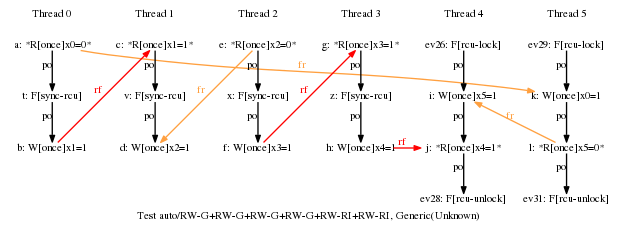

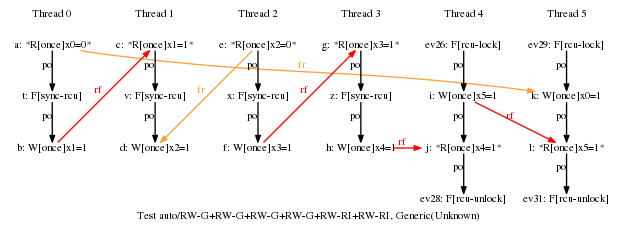

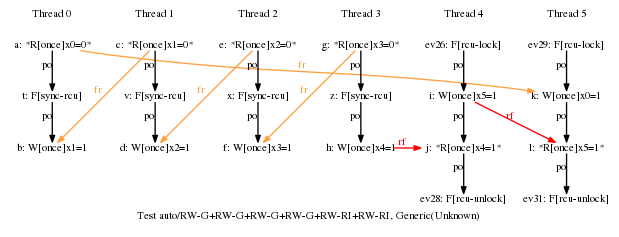

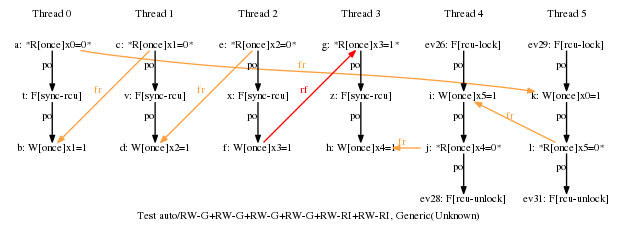

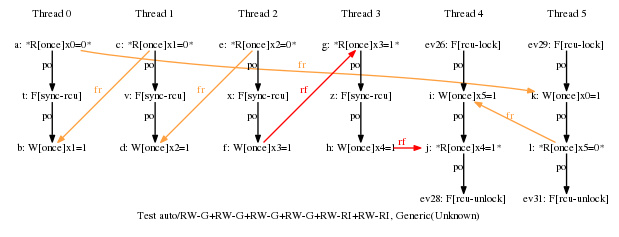

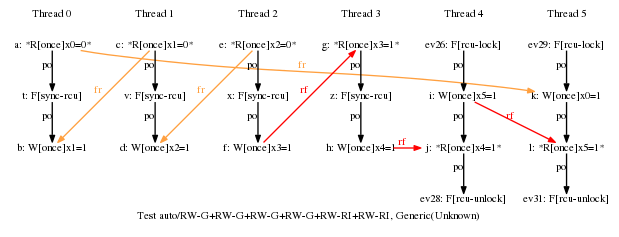

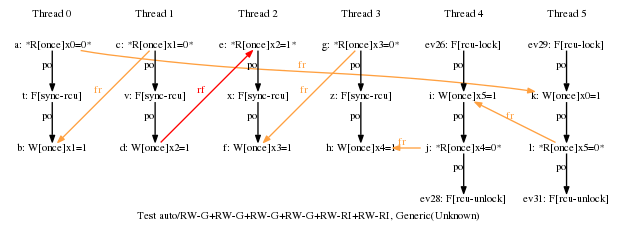

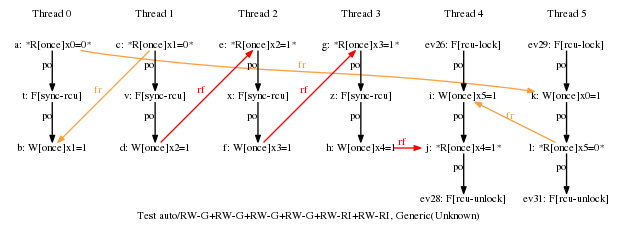

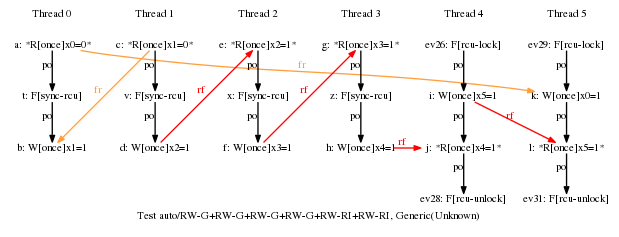

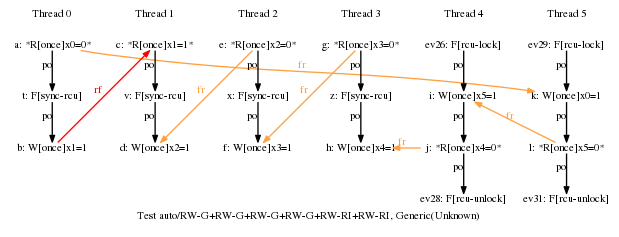

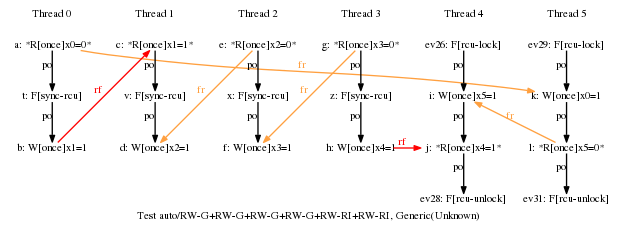

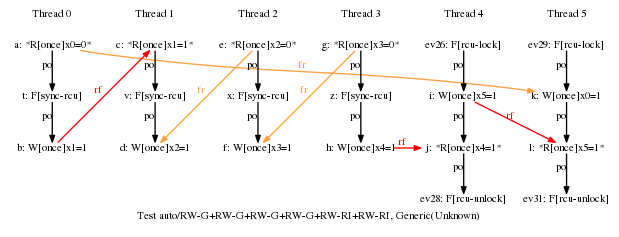

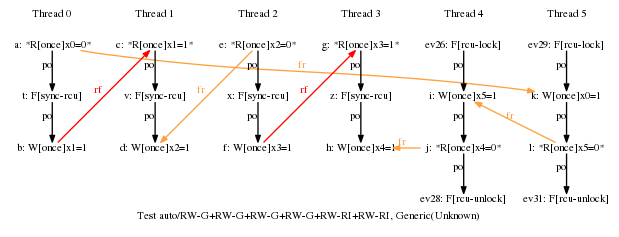

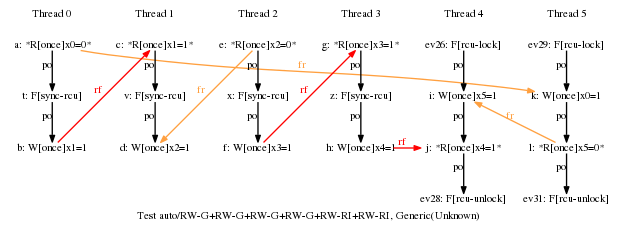

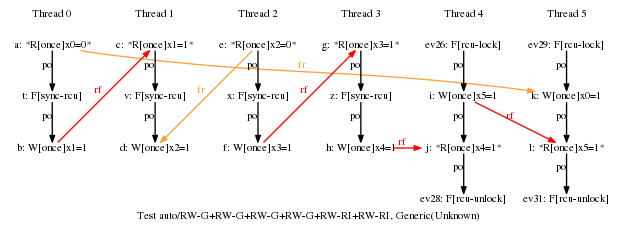

LISA auto/RW-G+RW-G+RW-G+RW-G+RW-RI+RW-RI

(*

* Result: Never

*

* Process 0 starts (t=100000).

*

* P0 advances one grace period (t=200000).

*

* P1 advances one grace period (t=300001).

*

* P2 advances one grace period (t=400002).

*

* P3 advances one grace period (t=500003).

*

* P4 goes back a bit less than one grace period (t=401004).

*

* P5 goes back a bit less than one grace period (t=302005).

*

* Process 0 start at t=100000, process 6 end at t=302005: Cycle forbidden.

*)

{

}

P0 | P1 | P2 | P3 | P4 | P5 ;

r[once] r1 x0 | r[once] r1 x1 | r[once] r1 x2 | r[once] r1 x3 | f[rcu_read_lock] | f[rcu_read_lock] ;

f[sync] | f[sync] | f[sync] | f[sync] | w[once] x5 1 | w[once] x0 1 ;

w[once] x1 1 | w[once] x2 1 | w[once] x3 1 | w[once] x4 1 | r[once] r1 x4 | r[once] r1 x5 ;

| | | | f[rcu_read_unlock] | f[rcu_read_unlock] ;

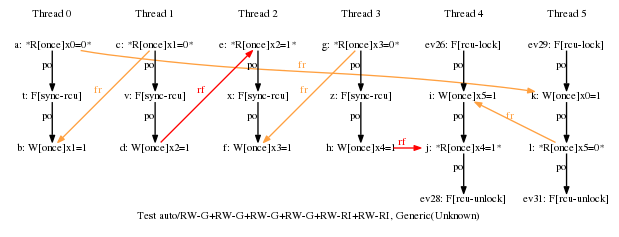

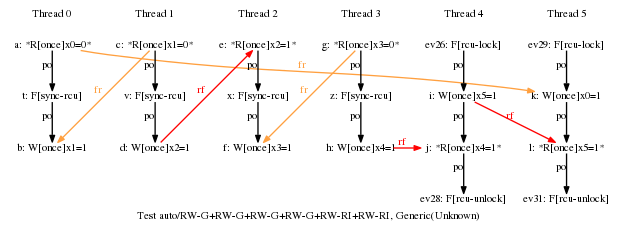

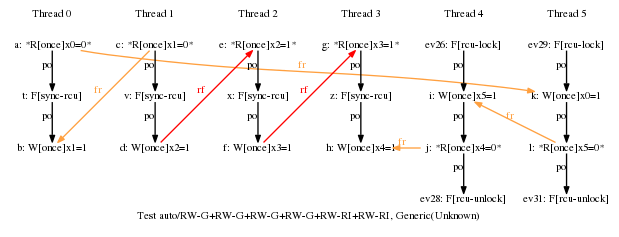

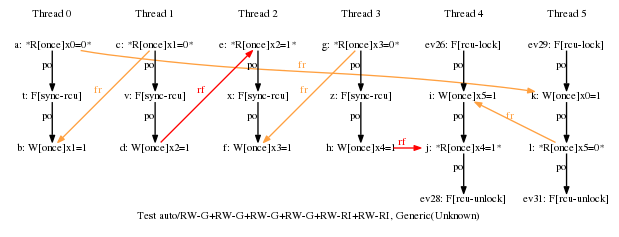

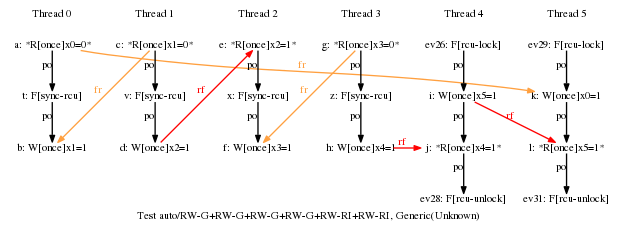

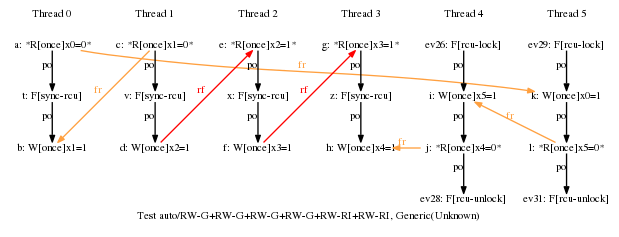

Observed

5:r1=0; 4:r1=1; 3:r1=1; 2:r1=1; 1:r1=1; 0:r1=1;

and 5:r1=1; 4:r1=1; 3:r1=0; 2:r1=1; 1:r1=1; 0:r1=1;

and 5:r1=0; 4:r1=1; 3:r1=0; 2:r1=1; 1:r1=1; 0:r1=1;

and 5:r1=1; 4:r1=1; 3:r1=1; 2:r1=0; 1:r1=1; 0:r1=1;

and 5:r1=0; 4:r1=1; 3:r1=1; 2:r1=0; 1:r1=1; 0:r1=1;

and 5:r1=1; 4:r1=1; 3:r1=0; 2:r1=0; 1:r1=1; 0:r1=1;

and 5:r1=0; 4:r1=1; 3:r1=0; 2:r1=0; 1:r1=1; 0:r1=1;

and 5:r1=1; 4:r1=1; 3:r1=1; 2:r1=1; 1:r1=0; 0:r1=1;

and 5:r1=0; 4:r1=1; 3:r1=1; 2:r1=1; 1:r1=0; 0:r1=1;

and 5:r1=1; 4:r1=1; 3:r1=0; 2:r1=1; 1:r1=0; 0:r1=1;

and 5:r1=1; 4:r1=1; 3:r1=1; 2:r1=0; 1:r1=0; 0:r1=1;

and 5:r1=1; 4:r1=1; 3:r1=0; 2:r1=0; 1:r1=0; 0:r1=1;

and 5:r1=0; 4:r1=1; 3:r1=0; 2:r1=0; 1:r1=0; 0:r1=1;

and 5:r1=1; 4:r1=1; 3:r1=1; 2:r1=1; 1:r1=1; 0:r1=0;

and 5:r1=0; 4:r1=1; 3:r1=1; 2:r1=1; 1:r1=1; 0:r1=0;

and 5:r1=0; 4:r1=0; 3:r1=1; 2:r1=1; 1:r1=1; 0:r1=0;

and 5:r1=1; 4:r1=1; 3:r1=0; 2:r1=1; 1:r1=1; 0:r1=0;

and 5:r1=0; 4:r1=1; 3:r1=0; 2:r1=1; 1:r1=1; 0:r1=0;

and 5:r1=0; 4:r1=0; 3:r1=0; 2:r1=1; 1:r1=1; 0:r1=0;

and 5:r1=1; 4:r1=1; 3:r1=1; 2:r1=0; 1:r1=1; 0:r1=0;

and 5:r1=0; 4:r1=1; 3:r1=1; 2:r1=0; 1:r1=1; 0:r1=0;

and 5:r1=0; 4:r1=0; 3:r1=1; 2:r1=0; 1:r1=1; 0:r1=0;

and 5:r1=1; 4:r1=1; 3:r1=0; 2:r1=0; 1:r1=1; 0:r1=0;

and 5:r1=0; 4:r1=1; 3:r1=0; 2:r1=0; 1:r1=1; 0:r1=0;

and 5:r1=0; 4:r1=0; 3:r1=0; 2:r1=0; 1:r1=1; 0:r1=0;

and 5:r1=1; 4:r1=1; 3:r1=1; 2:r1=1; 1:r1=0; 0:r1=0;

and 5:r1=0; 4:r1=1; 3:r1=1; 2:r1=1; 1:r1=0; 0:r1=0;

and 5:r1=0; 4:r1=0; 3:r1=1; 2:r1=1; 1:r1=0; 0:r1=0;

and 5:r1=1; 4:r1=1; 3:r1=0; 2:r1=1; 1:r1=0; 0:r1=0;

and 5:r1=0; 4:r1=1; 3:r1=0; 2:r1=1; 1:r1=0; 0:r1=0;

and 5:r1=0; 4:r1=0; 3:r1=0; 2:r1=1; 1:r1=0; 0:r1=0;

and 5:r1=1; 4:r1=1; 3:r1=1; 2:r1=0; 1:r1=0; 0:r1=0;

and 5:r1=0; 4:r1=1; 3:r1=1; 2:r1=0; 1:r1=0; 0:r1=0;

and 5:r1=0; 4:r1=0; 3:r1=1; 2:r1=0; 1:r1=0; 0:r1=0;

and 5:r1=1; 4:r1=1; 3:r1=0; 2:r1=0; 1:r1=0; 0:r1=0;

…

…