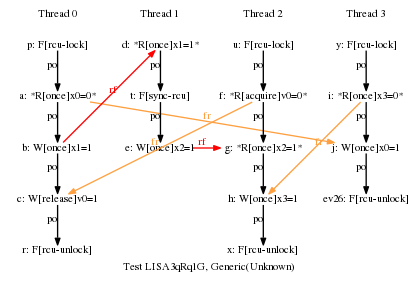

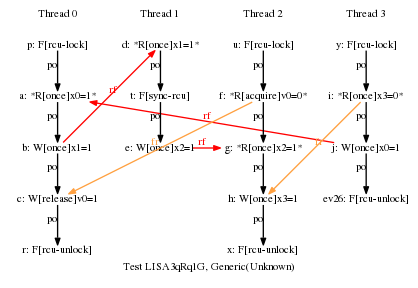

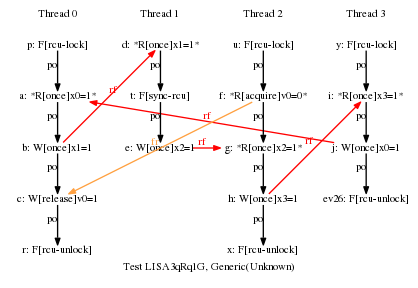

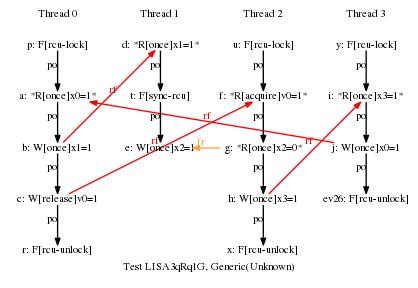

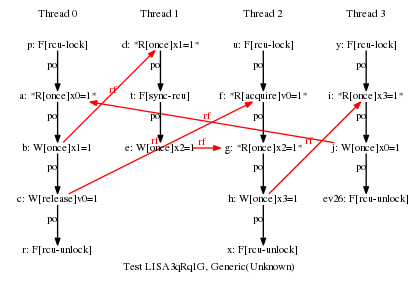

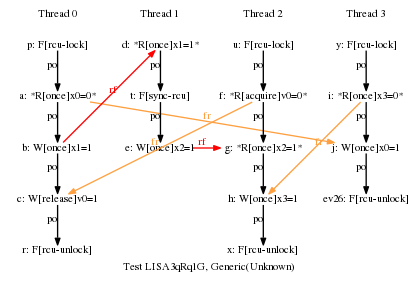

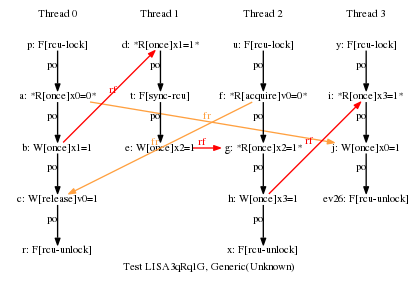

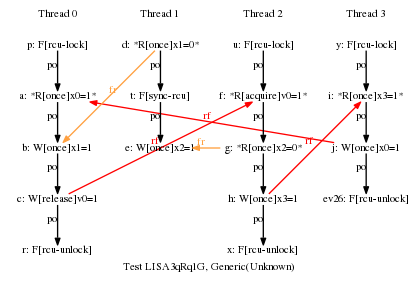

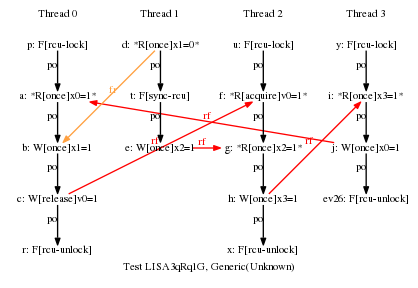

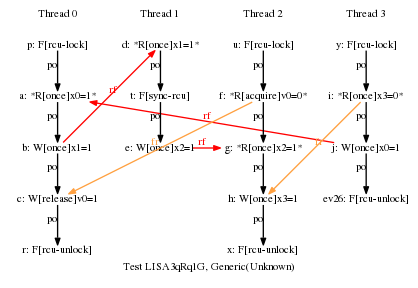

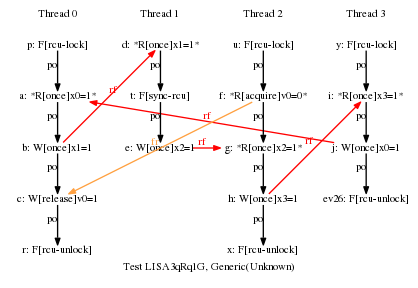

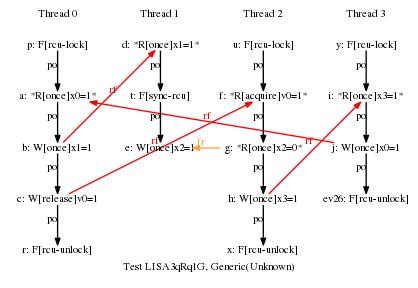

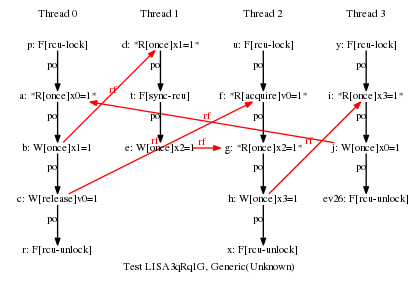

LISA LISA3qRq1G

(*

* Result: Sometimes

*

* One grace period and three RCU read-side critical sections.

* Ordering across a RCU grace period could prohibit cycles, except that

* P3's RCU read-side critical section still allows the needed misordering.

* The reason that this ordering is not completely redundant with the grace

* period is that it forces P0's critical section to precede that of P2.

* Cycle allowed.

*)

{

x0 = 0;

x1 = 0;

x2 = 0;

x3 = 0;

v0 = 0;

}

P0 | P1 | P2 | P3 ;

f[rcu_read_lock] | r[once] r1 x1 | f[rcu_read_lock] | f[rcu_read_lock] ;

r[once] r2 x0 | f[sync] | r[acquire] r4 v0 | r[once] r3 x3 ;

w[once] x1 1 | w[once] x2 1 | r[once] r2 x2 | w[once] x0 1 ;

w[release] v0 1 | | w[once] x3 1 | f[rcu_read_unlock] ;

f[rcu_read_unlock] | | f[rcu_read_unlock] | ;

Observed

3:r3=1; 2:r4=1; 2:r2=1; 1:r1=1; 0:r2=1;

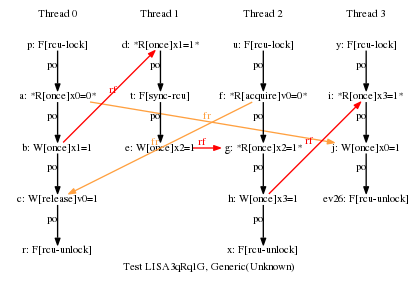

and 3:r3=1; 2:r4=0; 2:r2=1; 1:r1=1; 0:r2=1;

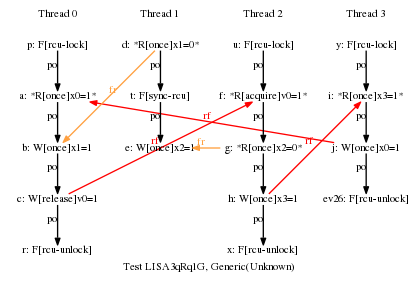

and 3:r3=0; 2:r4=0; 2:r2=1; 1:r1=1; 0:r2=1;

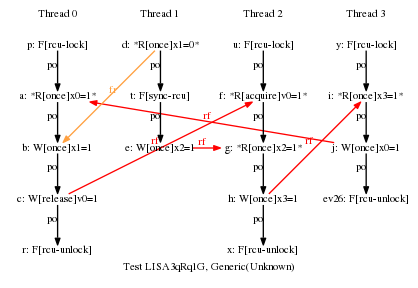

and 3:r3=1; 2:r4=1; 2:r2=0; 1:r1=1; 0:r2=1;

and 3:r3=1; 2:r4=1; 2:r2=1; 1:r1=0; 0:r2=1;

and 3:r3=1; 2:r4=1; 2:r2=0; 1:r1=0; 0:r2=1;

and 3:r3=1; 2:r4=0; 2:r2=1; 1:r1=1; 0:r2=0;

and 3:r3=0; 2:r4=0; 2:r2=1; 1:r1=1; 0:r2=0;