C WRW+2W+pooncerelease+fencemboncerelease+Release

Hash=e0e1f7679a1105570df1797f942712d6

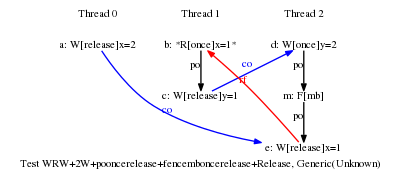

Cycle=PodRWOnceRelease WseReleaseOnce FenceMbdWWOnceRelease WseReleaseRelease RfeReleaseOnce

Relax=RfeReleaseOnce WseReleaseOnce WseReleaseRelease

Safe=FenceMbdWW PodRWOnceRelease

Generator=diy7 (version 7.46+3)

Prefetch=1:x=F,1:y=W,2:y=F,2:x=W

Com=Rf Ws Ws

Orig=RfeReleaseOnce PodRWOnceRelease WseReleaseOnce FenceMbdWWOnceRelease WseReleaseRelease

{}

P0(int* x) {

smp_store_release(x,2);

}

P1(int* x,int* y) {

int r0 = READ_ONCE(*x);

smp_store_release(y,1);

}

P2(int* x,int* y) {

WRITE_ONCE(*y,2);

smp_mb();

smp_store_release(x,1);

}

Observed

y=2; x=2; 1:r0=1;

and y=2; x=1; 1:r0=1;

C11 equivalent:

C WRW+2W+pooncerelease+fencemboncerelease+Release

Hash=e0e1f7679a1105570df1797f942712d6

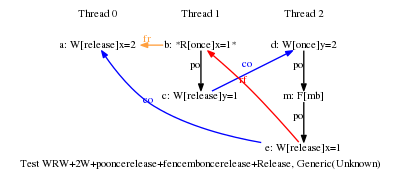

Cycle=PodRWOnceRelease WseReleaseOnce FenceMbdWWOnceRelease WseReleaseRelease RfeReleaseOnce

Relax=RfeReleaseOnce WseReleaseOnce WseReleaseRelease

Safe=FenceMbdWW PodRWOnceRelease

Generator=diy7 (version 7.46+3)

Prefetch=1:x=F,1:y=W,2:y=F,2:x=W

Com=Rf Ws Ws

Orig=RfeReleaseOnce PodRWOnceRelease WseReleaseOnce FenceMbdWWOnceRelease WseReleaseRelease

{}

P0(atomic_int* x) {

atomic_store_explicit(x,2,memory_order_release);

}

P1(atomic_int* x,atomic_int* y) {

int r0 = atomic_load_explicit(x,memory_order_relaxed);

atomic_store_explicit(y,1,memory_order_release);

}

P2(atomic_int* x,atomic_int* y) {

atomic_store_explicit(y,2,memory_order_relaxed);

atomic_thread_fence(memory_order_seq_cst);

atomic_store_explicit(x,1,memory_order_release);

}

exists (x=2 /\ y=2 /\ 1:r0=2)