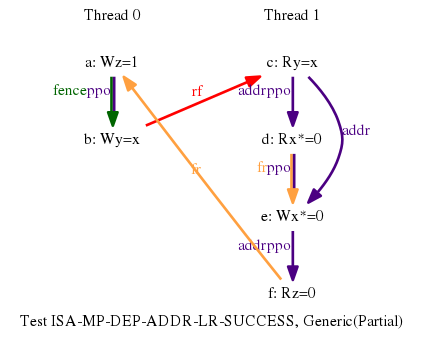

RISCV ISA-MP-DEP-ADDR-LR-SUCCESS

(*

In case the sc succeeds there is an address dependency from

P1 initial load to P1 final load. The dependency chain passes through

the "reservation" register.

*)

{

int z;

int *y = &z;

0:s3=z; 0:s2=y; 0:s1=x;

1:s3=z; 1:s2=y; 1:s1=x;

}

P0 | P1 ;

ori x5,x0,1 | ld a1,0(s2) ;

sw x5,0(s3) | lr.w t1,0(a1) ;

fence w,w | sc.w t2,x0,0(s1) ;

sd s1,0(s2) | xor t3,t2,t2 ;

| add s4,s3,t3 ;

| lw t4,0(s4) ;

~exists 1:a1=x /\ 1:t4=0 /\ 1:t2=0