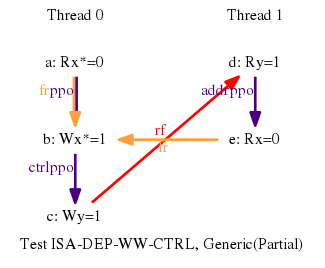

RISCV ISA-DEP-WW-CTRL

(* SC-W to W control dependency through result register *)

{

0:x5=x; 0:x10=y;

1:x6=y; 1:x9=x;

}

P0 | P1 ;

ori x6,x0,1 | lw x5,0(x6) ;

lr.w x7,0(x5) | andi x7,x5,2 ;

sc.w x8,x6,0(x5) | add x10,x9,x7 ;

bne x8,x0,LOUT | lw x8,0(x10) ;

ori x1,x0,1 | ;

sw x1,0(x10) | ;

LOUT: | ;

exists

(x=1 /\ 1:x5=1 /\ 1:x8=0)