…

…

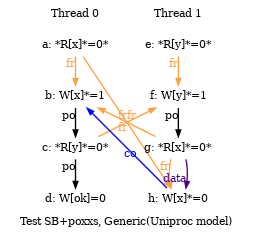

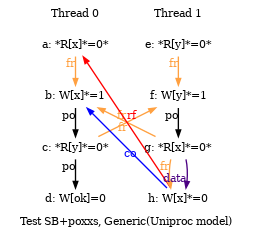

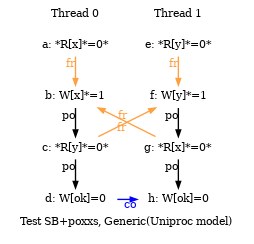

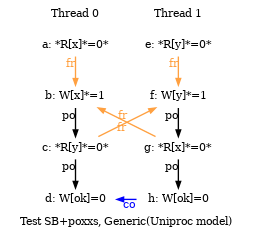

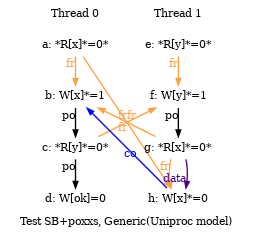

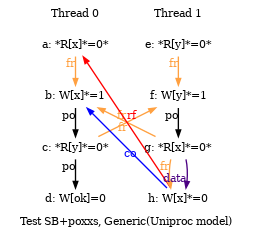

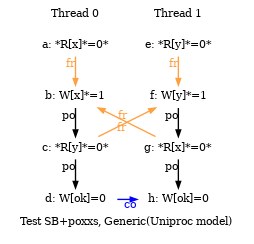

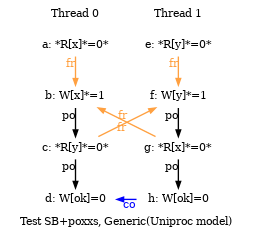

AArch64 SB+poxxs

"PodWRXX FreXX PodWRXX FreXX"

Cycle=FreXX PodWRXX FreXX PodWRXX

Relax=

Safe=PodWR FreXX

Prefetch=0:x=F,0:y=T,1:y=F,1:x=T

Com=Fr Fr

Orig=PodWRXX FreXX PodWRXX FreXX

{ ok=1;

0:X0=x; 0:X4=y; 0:X7=ok;

1:X0=y; 1:X4=x; 1:X7=ok;

}

P0 | P1 ;

MOV W1,#1 | MOV W1,#1 ;

LDXR W2,[X0] | LDXR W2,[X0] ;

STXR W3,W1,[X0] | STXR W3,W1,[X0] ;

CBNZ W3,Fail0 | CBNZ W3,Fail1 ;

LDXR W5,[X4] | LDXR W5,[X4] ;

STXR W3,W5,[X4] | STXR W3,W5,[X4] ;

CBNZ W3,Fail0 | CBNZ W3,Fail1 ;

B Exit0 | B Exit1 ;

Fail0: | Fail1: ;

MOV W6,#0 | MOV W6,#0 ;

STR W6,[X7] | STR W6,[X7] ;

Exit0: | Exit1: ;

Observed

y=1; x=1; ok=1; 1:X5=0; 1:X2=0; 0:X5=0; 0:X2=0;

and y=1; x=1; ok=0; 1:X5=0; 1:X2=0; 0:X5=0; 0:X2=0;

…

…