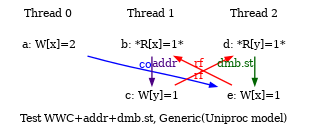

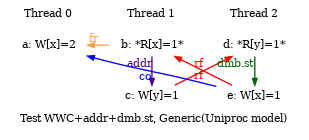

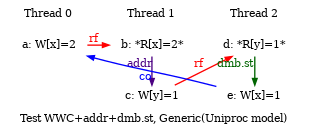

AArch64 WWC+addr+dmb.st

"Rfe DpAddrdW Rfe DMB.STdRW Wse"

Cycle=Rfe DMB.STdRW Wse Rfe DpAddrdW

Relax=

Safe=Rfe Wse DMB.STdRW DpAddrdW

Prefetch=1:x=F,1:y=W,2:y=F,2:x=W

Com=Rf Rf Ws

Orig=Rfe DpAddrdW Rfe DMB.STdRW Wse

{

0:X1=x;

1:X1=x; 1:X4=y;

2:X1=y; 2:X3=x;

}

P0 | P1 | P2 ;

MOV W0,#2 | LDR W0,[X1] | LDR W0,[X1] ;

STR W0,[X1] | EOR W2,W0,W0 | DMB ST ;

| MOV W3,#1 | MOV W2,#1 ;

| STR W3,[X4,W2,SXTW] | STR W2,[X3] ;

Observed

x=2; 2:X0=1; 1:X0=2;

and x=2; 2:X0=1; 1:X0=1;

and x=1; 2:X0=1; 1:X0=1;