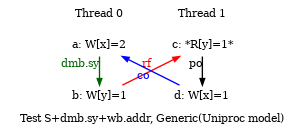

AArch64 S+dmb.sy+wb.addr

{

0:X1=x; 0:X3=y;

1:X1=y; 1:X3=x;

}

P0 | P1 ;

MOV W0,#2 | LDR W0,[X1],#4 ;

STR W0,[X1] | EOR X2,X1,X1 ;

DMB SY | MOV W4,#1 ;

MOV W2,#1 | STR W4,[X3,X2] ;

STR W2,[X3] | ;

Observed

x=2; 1:X0=1;