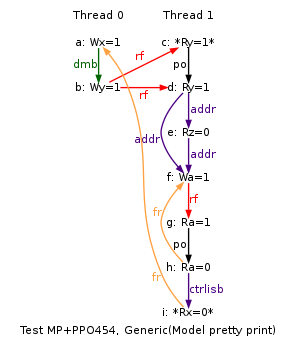

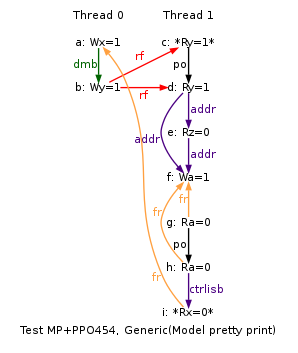

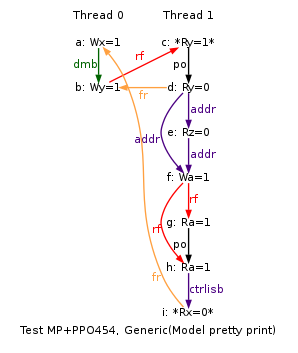

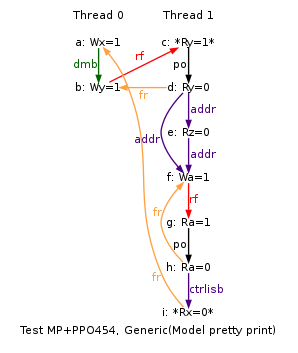

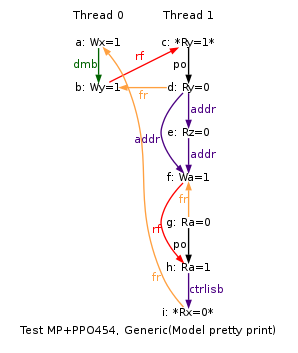

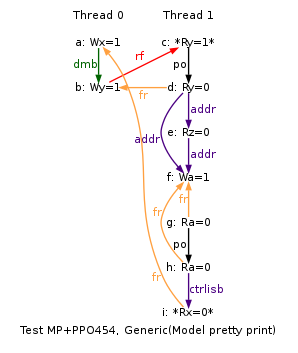

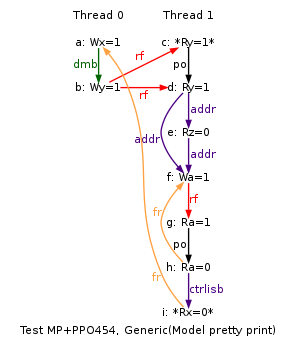

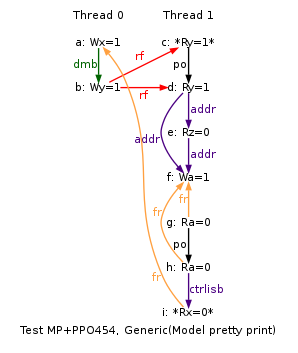

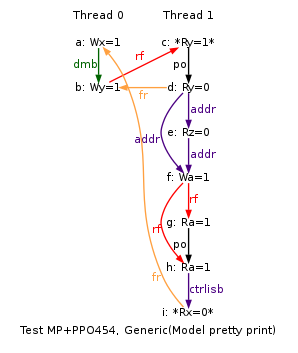

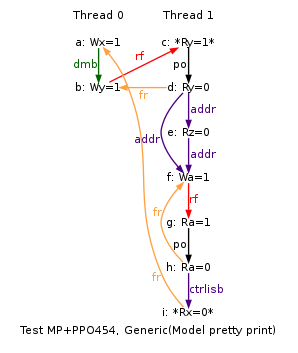

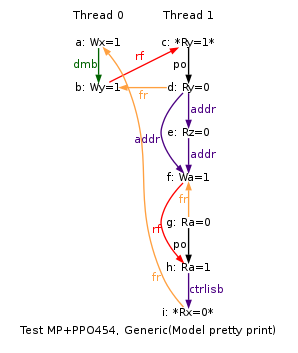

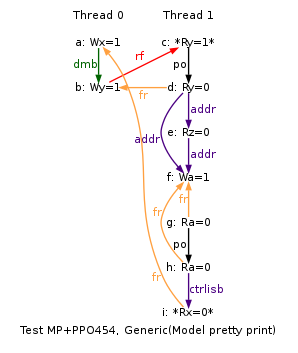

Executions for behaviour: "1:R0=1 ; 1:R8=0"

ARM MP+PPO454

"Fre DMBdWW Rfe PosRR DpAddrdR DpAddrdW PosWR PosRR DpCtrlIsbdR"

Cycle=Rfe PosRR DpAddrdR DpAddrdW PosWR PosRR DpCtrlIsbdR Fre DMBdWW

Relax=

Safe=Rfe Fre PosWR PosRR DMBdWW DpAddrdW DpAddrdR DpCtrlIsbdR

Prefetch=1:x=T

Orig=Fre DMBdWW Rfe PosRR DpAddrdR DpAddrdW PosWR PosRR DpCtrlIsbdR

{

%x0=x; %y0=y;

%y1=y; %z1=z; %a1=a; %x1=x;

}

P0 | P1 ;

MOV R0, #1 | LDR R0, [%y1] ;

STR R0, [%x0] | LDR R1, [%y1] ;

DMB | EOR R2,R1,R1 ;

MOV R1, #1 | LDR R3, [R2,%z1] ;

STR R1, [%y0] | EOR R4,R3,R3 ;

| MOV R5, #1 ;

| STR R5, [R4,%a1] ;

| LDR R6, [%a1] ;

| LDR R7, [%a1] ;

| CMP R7, R7 ;

| BNE LC00 ;

| LC00: ;

| ISB ;

| LDR R8, [%x1] ;

Observed

1:R0=1; 1:R8=0;