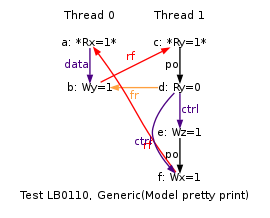

Executions for behaviour:

"0:R0=1 ; 1:R0=1"

ARM LB0110

"DpDatadW Rfe PosRR DpCtrldW PodWW Rfe"

Cycle=Rfe PosRR DpCtrldW PodWW Rfe DpDatadW

Relax=[Rfe,DpDatadW,Rfe]

Safe=PosRR PodWW DpCtrldW

Prefetch=0:x=F,0:y=W,1:y=F,1:x=W

Com=Rf Rf

Orig=DpDatadW Rfe PosRR DpCtrldW PodWW Rfe

{

%x0=x; %y0=y;

%y1=y; %z1=z; %x1=x;

}

P0 | P1 ;

LDR R0,[%x0] | LDR R0,[%y1] ;

EOR R1,R0,R0 | LDR R1,[%y1] ;

ADD R1,R1,#1 | CMP R1,R1 ;

STR R1,[%y0] | BNE LC00 ;

| LC00: ;

| MOV R2,#1 ;

| STR R2,[%z1] ;

| MOV R3,#1 ;

| STR R3,[%x1] ;

Observed

0:R0=1; 1:R0=1;