| Model | Tegra2 | APQ8060 | A5X | A6X | Exynos5250 | Tegra3 | Exynos4412 | Exynos5410 | APQ8064 | |

| CoRR | Forbid | 4/20G | 0/8.6G | 1.0k/3.7G | 0/14G | 0/8.3G | 5/2.7G | 163/11G | 0/6.3G | 0/7.5G |

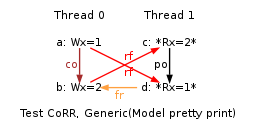

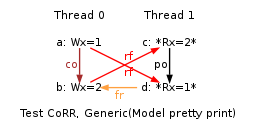

Executions for behaviour: "1:R0=2 ; 1:R1=1"

ARM CoRR

{0:R2=x; 1:R2=x;}

P0 | P1 ;

MOV R0,#1 | LDR R0,[R2] ;

STR R0,[R2] | LDR R1,[R2] ;

MOV R1,#2 | ;

STR R1,[R2] | ;

exists (1:R0=2 /\ 1:R1=1)