| Model | Tegra3 | Exynos4412 | Exynos5410 | APQ8064 | |

| MP+dmb+fri-rfi-ctrlisb+BIS | Forbid | Ok, 29/11G | No, 0/14G | No, 0/3.1G | No, 0/2.3G |

| Allow unseen | Allow unseen | Allow unseen |

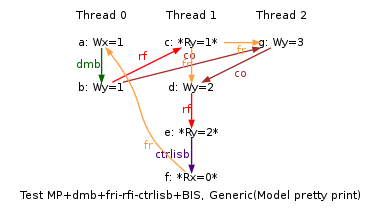

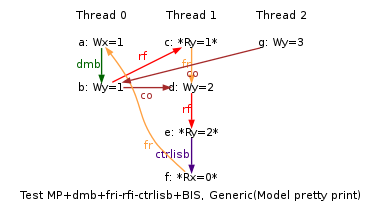

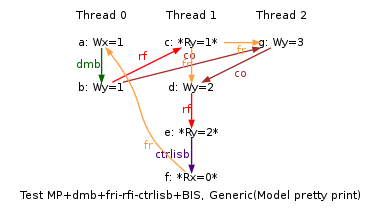

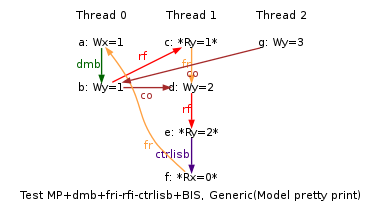

Executions for behaviour:

"1:R0=1 ; 1:R2=2 ; 1:R3=0 ; y=2"

ARM MP+dmb+fri-rfi-ctrlisb+BIS

"DMBdWW Rfe Fri Rfi DpCtrlIsbdR Fre + Some write

Prefetch=0:x=F,0:y=W,1:y=F,1:x=T

Com=Rf Fr

Orig=DMBdWW Rfe Fri DetourW DpCtrlIsbdR Fre

{

%x0=x; %y0=y;

%y1=y; %x1=x;

%y2=y;

}

P0 | P1 | P2 ;

MOV R0,#1 | LDR R0,[%y1] | MOV R0,#3 ;

STR R0,[%x0] | MOV R1,#2 | STR R0,[%y2] ;

DMB | STR R1,[%y1] | ;

MOV R1,#1 | LDR R2,[%y1] | ;

STR R1,[%y0] | CMP R2,R2 | ;

| BNE LC00 | ;

| LC00: | ;

| ISB | ;

| LDR R3,[%x1] | ;

Observed

1:R0=1; 1:R2=2; 1:R3=0; y=2;